JEDEC JESD22B113

चुनौती

बोर्ड स्तर यांत्रिक परीक्षण माइक्रोइलेक्ट्रॉनिक पैकेजिंग उद्योग के भीतर एक आवश्यक गुणवत्ता नियंत्रण परीक्षण है। वे शिपमेंट के दौरान और अंत-उपयोग वाले उत्पादों में इंटरकनेक्ट विफलताओं के खिलाफ आईसी घटकों के प्रदर्शन का समर्थन करने के लिए परीक्षण डेटा प्रदान करते हैं जहां चक्रीय तनाव और प्रभाव से झटका अनुभव होता है।

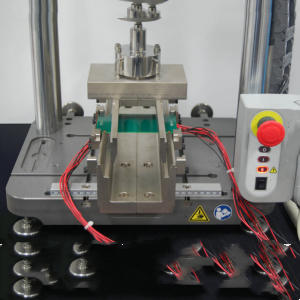

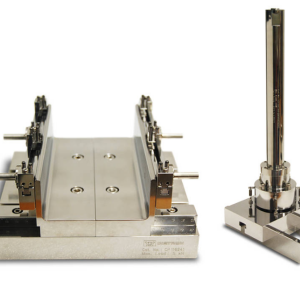

JEDEC JESD22B113 परीक्षण विधि का उपयोग हाथ में इलेक्ट्रॉनिक उत्पाद अनुप्रयोगों के लिए एक त्वरित परीक्षण वातावरण में सतह पर चढ़े इलेक्ट्रॉनिक घटकों के प्रदर्शन का मूल्यांकन और तुलना करने के लिए किया जाता है। यह एक निर्दिष्ट 4-बिंदु चक्रीय झुकने परीक्षण विधि का उपयोग करके किया जाता है।

हमारा समाधान

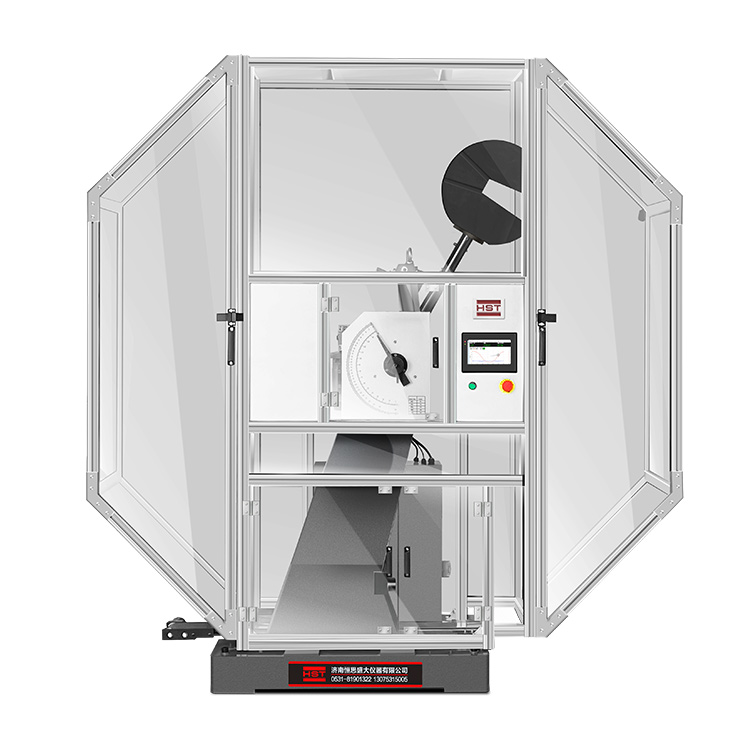

मानक एक ड्रॉप इम्पैक्ट टेस्ट के लिए आकार और लेआउट के समान एक नमूना डिजाइन की सिफारिश करता है। यह इस परीक्षण को करने के लिए स्पैन और चक्रीय आयाम, आवृत्ति और तरंगों को निर्दिष्ट करता है। इंटरकनेक्शन की विफलता प्रतिरोध डेज़ी श्रृंखलाओं के आधार पर निर्धारित की जाती है, आमतौर पर प्रारंभिक प्रतिरोध या 1000OHM का पांच गुना, जो भी अधिक हो। JEDEC JESD22B113 परीक्षण की चुनौती कि एक ऑपरेटर के पास परीक्षण प्रणाली को लगातार 4-बिंदु मोड़ के माध्यम से मुद्रित वायरिंग बोर्ड (PWB) पर एक निर्दिष्ट चक्रीय तरंग के आधार पर फ्लेक्सुरल लोडिंग उत्पन्न करना होगा, जो लंबे समय तक थकान तक-1-3Hz आवृत्ति के बिना 200,000 चक्रों तक।